이전 글에서 작성했던 것처럼 FlipFlop은 Latch에 edge detector circuit을 붙여서 사용합니다.

이번 F/F 설명부터는 edge detector circuit을 생략하겠습니다.

D Latch (FlipFlop)

Latch의 경우 CLK가 1이면 Q <= D

F/F의 경우 CLK가 rising edge이면 Q <= D

이외에는 Q hold

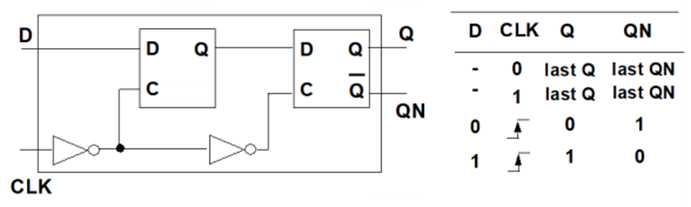

Master/Slave D FlipFlop

D Latch 2개로 구성되어 있는 M/S FlipFlop입니다.

이 경우 CLK에 inverter가 있어서 0.5주기의 delay 발생합니다.

대신, race 현상이 일부 해결되고 1'st catching problem이 해결됩니다.

Verilog Code

D FlipFlop을 verilog로 설계하였습니다.

이번에는 clock과 reset을 이용하였습니다.

DUT

`timescale 1ns / 1ps

module dff(

i_clk,

i_reset,

i_d,

o_q

);

input i_clk;

input i_reset;

input i_d;

output reg o_q;

always @ (posedge i_clk or negedge i_reset) begin

if (!i_reset) begin

o_q <= 1'b0;

end

else begin

o_q <= i_d;

end

end

endmodule

Testbench

`timescale 1ns / 1ps

module tb_dff();

reg i_clk;

reg i_reset;

reg i_d;

wire o_q;

dff dff ( .i_clk (i_clk) ,

.i_reset (i_reset),

.i_d (i_d) ,

.o_q (o_q) );

always #5 i_clk = ~i_clk;

initial begin

i_clk = 1'b0; i_reset = 1'b1;

i_d = 1'b0; #1

i_reset = 1'b0; #1

i_reset = 1'b1; #5

i_d = 1'b1; #10

i_d = 1'b0; #10

i_d = 1'b1; #10

$finish;

end

endmodule

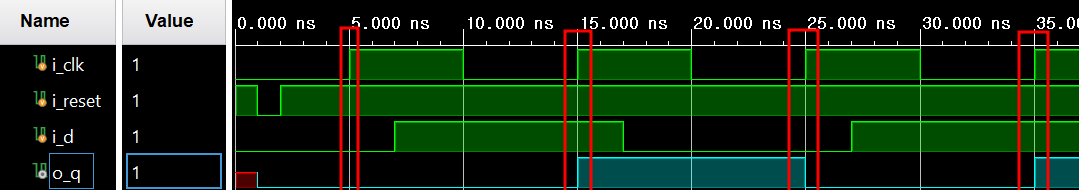

Simulation

FlipFlop이므로 rising edge에서만 값이 update되는 것을 볼 수 있습니다.

'Digital Design > 논리회로' 카테고리의 다른 글

| [논리회로] T Latch와 FlipFlop (1) | 2023.01.06 |

|---|---|

| [논리회로] JK Latch와 FlipFlop (1) | 2023.01.06 |

| [논리회로] SR Latch와 FlipFlop (1) | 2023.01.02 |

| [논리회로] Latch와 FlipFlop의 차이 (1) | 2023.01.02 |

| [논리회로] Synchronous, Asynchronous (1) | 2023.01.02 |

댓글