이전 글에서 작성했던 것처럼 FlipFlop은 Latch에 edge detector circuit을 붙여서 사용합니다.

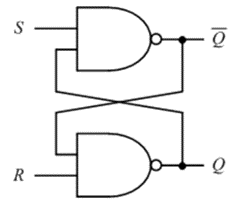

SR Latch with NAND

S는 set, R은 reset을 의미합니다.

| INPUT | OUTPUT | ||

| S | R | Q | Qb |

| 0 | 0 | 1 (금지) | 1 (금지) |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | Q (유지) | Qb (유지) |

S와 R이 0일 때는 (1, 1)이 나오지만 Q = Qb가 되어버리므로 타당한 값이 아닙니다.

S와 R이 1일 때는 이전 값을 그대로 사용합니다.

SR이 (1, 1)에서 (0, 0)이 되면 (1, 1) -> (0, 0) -> (1, 1) -> (0, 0) -> ···

으로 발진하는 Race 현상이 발생합니다.

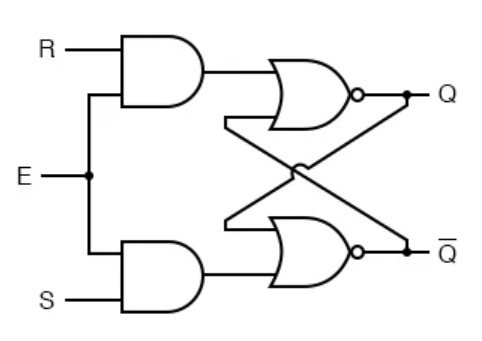

Gated SR Latch

| INPUT | OUTPUT | |||

| CP | R | S | Q | Qb |

| 0 | - | - | 유지 | |

| 1 | 0 | 0 | 유지 | |

| 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | |

| 1 | 1 | 금지 | ||

Gated Latch는 AND gate를 이용하여 Latch에 enable을 붙인 것입니다.

Enable이 Low이면 (0, 0)이 들어가므로 이전 상태를 유지합니다.

SR FlipFlop

이렇게 edge detector circuit을 붙여주어야 FlipFlop 역할을 할 수 있습니다.

edge 구간에서만 값을 update 하므로 glitch에 보다 안정적입니다.

'Digital Design > 논리회로' 카테고리의 다른 글

| [논리회로] JK Latch와 FlipFlop (1) | 2023.01.06 |

|---|---|

| [논리회로] D Latch와 FlipFlop (Design with Verilog) (1) | 2023.01.02 |

| [논리회로] Latch와 FlipFlop의 차이 (1) | 2023.01.02 |

| [논리회로] Synchronous, Asynchronous (1) | 2023.01.02 |

| [논리회로] Combinational Circuit, Sequential Circuit (1) | 2023.01.02 |

댓글