논리회로에서 중요한 회로인 카운터 (Counter) 에 대한 글입니다.

RTL로 설계를 할 때, 카운터는 자주 쓰이는 회로입니다.

카운터의 동작만 잘 알아두어도 설계를 할 때 유용하게 쓸 수 있다고 합니다.

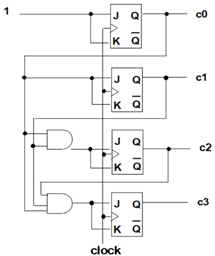

Synchronous Counter (동기식 카운터)

JK FlipFlop으로 이루어진 동기식 카운터입니다.

Synchronous Counter는 비동기식보단 복잡하지만 빠르다는 장점이 있습니다.

Asynchronous Counter (비동기식 카운터)

JK FlipFlop으로 구성된 비동기식 카운터입니다.

Synchronous Counter보다 간단하지만 clock에 의해 동작하지 않으므로 느릴 수 있습니다.

비동기식 카운터는 Ripple Counter라고 부르기도 합니다.

앞 F/F의 출력을 뒤 F/F의 입력에 연결하여 값이 계속 toggle되는 형식으로 작동합니다.

Verilog Code

Counter를 Verilog로 설계하였습니다.

DUT

`timescale 1ns / 1ps

module counter(

i_clk,

i_reset,

o_cnt

);

input i_clk;

input i_reset;

output reg [3:0] o_cnt;

always @ (posedge i_clk or negedge i_reset) begin

if (!i_reset) begin

o_cnt <= 4'b0;

end

else begin

o_cnt <= o_cnt + 4'b1;

end

end

endmodule

Testbench

`timescale 1ns / 1ps

module tb_counter();

reg i_clk;

reg i_reset;

wire [3:0] o_cnt;

counter cnt ( .i_clk (i_clk) ,

.i_reset (i_reset) ,

.o_cnt (o_cnt) );

always #5 i_clk = ~i_clk;

initial begin

i_clk = 1'b0; i_reset = 1'b1; #1

i_reset = 1'b0; #1

i_reset = 1'b1;

#180

$finish;

end

endmodule

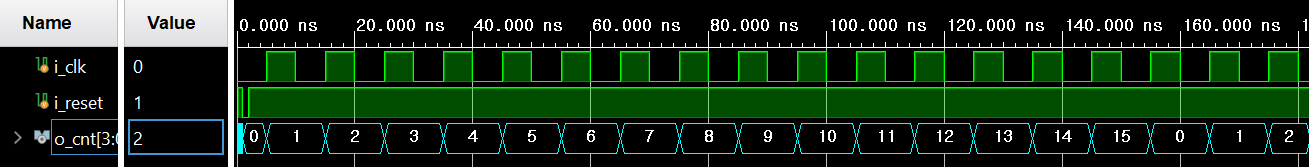

Simulation

카운터가 다 돌았을 때 어떻게 할 지 따로 작성하지 않았기 때문에

0으로 초기화되는 것을 볼 수 있습니다.

'Digital Design > 논리회로' 카테고리의 다른 글

| [논리회로] Register (Design with Verilog) (1) | 2023.01.07 |

|---|---|

| [논리회로] T Latch와 FlipFlop (1) | 2023.01.06 |

| [논리회로] JK Latch와 FlipFlop (1) | 2023.01.06 |

| [논리회로] D Latch와 FlipFlop (Design with Verilog) (1) | 2023.01.02 |

| [논리회로] SR Latch와 FlipFlop (1) | 2023.01.02 |

댓글