이번에 다룰 회로는 Multiplexer, MUX 입니다.

MUX는 2^N개의 입력을 N개의 select 신호에 따라 선택하는 모듈입니다.

4 to 1 MUX의 진리표 먼저 보겠습니다.

| INPUT | OUTPUT | |

| S0 | S1 | Y |

| 0 | 0 | I0 |

| 0 | 1 | I1 |

| 1 | 0 | I2 |

| 1 | 1 | I3 |

Y = s0's1'I0 + s0's1I1 + s0s1'I2 + s0s1I3

이 결과를 게이트로 나타내보겠습니다.

※ Demux

Demultiplexer는 MUX와 반대입니다.

1개의 input을 n개의 select 신호를 이용해 2^n개의 출력을 만들어냅니다.

마치 디코더와 같은 모양인데 enable이 1개의 input 역할을 한다고 보면 됩니다.

MUX와 DEMUX를 사용하는 이유는,

여러 입력을 하나의 데이터 스트림으로 병합할 수 있기 때문인데요

이렇게 함께 쓴다면 편리한 것은 물론 비용절감의 효과도 있습니다.

Verilog Code

4 to 1 MUX를 verilog로 설계하였습니다.

DUT

`timescale 1ns / 1ps

module mux_4to1(

i_clk,

i_in,

i_sel,

o_y

);

input i_clk;

input [3:0] i_in;

input [1:0] i_sel;

output reg o_y;

always @ (posedge i_clk) begin

case (i_sel)

2'b00: o_y = i_in[0];

2'b01: o_y = i_in[1];

2'b10: o_y = i_in[2];

2'b11: o_y = i_in[3];

default: o_y = 1'b0;

endcase

end

endmodule

Testbench

`timescale 1ns / 1ps

module tb_mux_4to1();

reg i_clk;

reg [3:0] i_in;

reg [1:0] i_sel;

wire o_y;

mux_4to1 mux ( .i_clk (i_clk) ,

.i_in (i_in) ,

.i_sel (i_sel) ,

.o_y (o_y) );

always #5 i_clk = ~i_clk;

initial begin

i_clk = 1'b0;

i_in = 4'b0101; i_sel = 2'b00; #10

i_sel = 2'b10; #10

i_in = 4'b1100; i_sel = 2'b01; #10

i_sel = 2'b11; #10

$finish;

end

endmodule

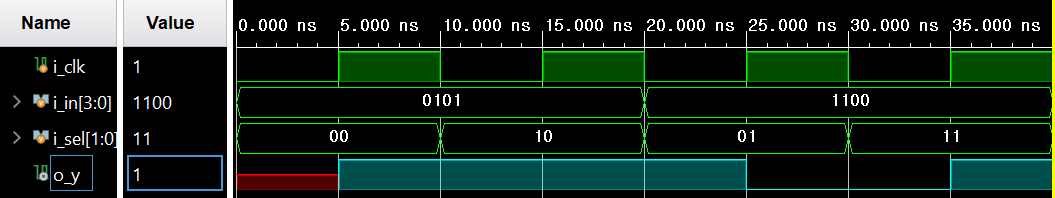

Simulation

'Digital Design > 논리회로' 카테고리의 다른 글

| [논리회로] Synchronous, Asynchronous (1) | 2023.01.02 |

|---|---|

| [논리회로] Combinational Circuit, Sequential Circuit (1) | 2023.01.02 |

| [논리회로] Decoder (Design with Verilog) (1) | 2023.01.02 |

| [논리회로] Full Subtractor (Design with Verilog) (1) | 2023.01.02 |

| [논리회로] Half Subtractor (Design with Verilog) (1) | 2022.12.30 |

댓글