첫 논리회로이기 때문에 과정까지 작성하였습니다.

Half Adder는 Input인 X와 Y를 더했을 때, 합은 Sum 올림은 Carry로 나타내 줍니다.

먼저 진리표를 보겠습니다.

| INPUT | OUTPUT | ||

| X | Y | Carry | Sum |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Half Adder는 간단하기 때문에 따로 카르노맵을 그리지 않아도 쉽게 구할 수 있습니다.

Carry의 경우, Input이 모두 1일 때 1이 출력됩니다.

따라서 AND 연산임을 알 수 있겠죠?

Carry = XY

Sum의 경우 두 Input이 서로 다를 때 1을 출력하고 있습니다.

따라서 XOR 연산임을 알 수 있습니다.

Sum = X ⊕ Y = X'Y + XY'

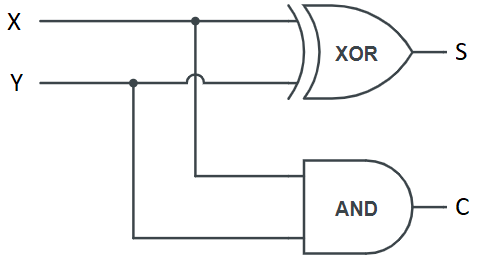

이제 게이트로 회로를 구성해 보겠습니다.

Verilog Code

이제 Half Adder를 Verilog HDL로 설계해보겠습니다.

저는 Xillinx 사의 Vivado를 이용해 디자인하였습니다.

DUT

`timescale 1ns / 1ps

module half_adder(

i_x,

i_y,

o_sum,

o_carry

) ;

input i_x;

input i_y;

output o_sum;

output o_carry;

assign o_sum = i_x ^ i_y;

assign o_carry = i_x & i_y;

endmodule

Testbench

`timescale 1ns / 1ps

module tb_half_adder();

reg i_x;

reg i_y;

wire o_sum;

wire o_carry;

half_adder ha( .i_x (i_x) ,

.i_y (i_y) ,

.o_sum (o_sum) ,

.o_carry (o_carry) );

initial begin

i_x = 1'b0; i_y = 1'b0; #10

i_x = 1'b0; i_y = 1'b1; #10

i_x = 1'b1; i_y = 1'b0; #10

i_x = 1'b1; i_y = 1'b1; #10

$finish;

end

Simulation

결과를 보면 진리표와 같은 값이 나온 것을 확인할 수 있습니다.

※ 참고로 assign문을 선언할 때는 결합연산자를 이용할 수도 있습니다.

assign {o_carry, o_sum} = {1'b0, i_x} + {1'b0, i_y};

'Digital Design > 논리회로' 카테고리의 다른 글

| [논리회로] Full Subtractor (Design with Verilog) (1) | 2023.01.02 |

|---|---|

| [논리회로] Half Subtractor (Design with Verilog) (1) | 2022.12.30 |

| [논리회로] Full Adder (Design with Verilog) (1) | 2022.12.29 |

| [논리회로] 여러가지 게이트(Gate) 2 (1) | 2022.12.29 |

| [논리회로] 여러가지 게이트(Gate) 1 (3) | 2022.12.29 |

댓글